一、引言:集成电路设计全景概览

集成电路(IC)设计是一个复杂且精密的过程,通常分为前端设计和后端设计两大核心阶段。前端设计聚焦于芯片的逻辑功能、架构定义和寄存器传输级(RTL)设计,而后端设计则是将前端输出的逻辑网表转化为可用于制造的物理版图(GDSII文件)的关键环节。随着半导体工艺节点不断演进至纳米级别,后端设计的复杂性和重要性日益凸显,成为决定芯片性能、功耗、面积(PPA)和最终上市时间(Time-to-Market)的决定性因素。本课件旨在系统介绍集成电路后端设计的基本流程、核心技术及其在整体芯片设计与服务生态中的角色。

二、集成电路后端设计核心流程

后端设计是一个多步骤、迭代优化的物理实现过程,主要包括以下阶段:

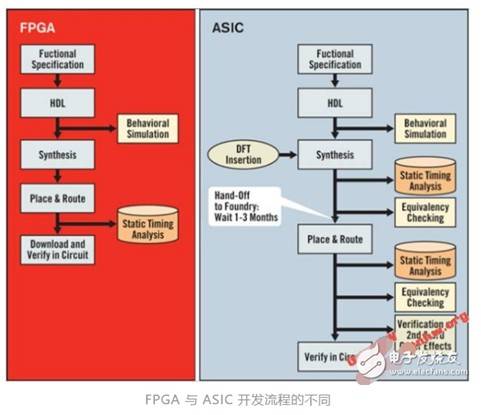

- 逻辑综合与可测性设计插入:使用综合工具将RTL代码转换为基于目标工艺库的门级网表。为了确保芯片的可测试性,会插入扫描链(Scan Chain)等DFT(Design for Test)结构。

- 布图规划与电源规划:

- 布图规划:确定芯片核心区域(Core Area)、输入输出(I/O)单元、宏模块(如存储器、IP核)的摆放位置,为后续布局布线提供基础框架。目标是优化芯片面积、信号完整性和时序性能。

- 电源规划:设计全局和局部电源/地线网络,确保整个芯片供电均匀、稳定,压降(IR Drop)和电迁移(EM)符合要求。

- 布局:将综合后的标准单元(Standard Cell)放置到芯片核心区域内。需考虑单元间的连接关系、时序路径、拥塞程度和功耗分布,进行初步优化。

- 时钟树综合:构建一个低偏斜(Skew)、低功耗的全局时钟分布网络,确保时钟信号能同步、可靠地送达所有时序单元(如触发器)。这是影响芯片性能和稳定性的关键步骤。

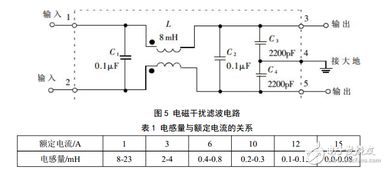

- 布线:根据逻辑连接关系,在多层金属互连层上完成所有标准单元、宏模块和I/O单元之间的物理连接。需解决信号完整性(如串扰)、设计规则检查(DRC)和电气规则检查(ERC)等问题。

- 物理验证与签核:

- 物理验证:对最终版图进行严格的DRC、LVS(版图与原理图一致性检查)和ERC检查,确保其符合晶圆厂的制造规则。

- 签核分析:进行最终、最精确的时序分析(STA)、功耗分析、信号完整性分析和可靠性分析(如EM/IR),确保设计在所有工艺角(Corner)和环境下都能满足性能、功耗和可靠性指标。

- 流片数据准备:生成最终交付给晶圆厂进行光刻制造的GDSII格式版图文件及相关文档。

三、后端设计中的关键技术挑战与趋势

- 先进工艺挑战:在7nm、5nm及以下节点,物理效应(如短沟道效应、量子隧穿)和工艺变异(PVT)的影响加剧,对时序收敛、功耗管理和可靠性设计提出极致要求。

- 多物理场协同优化:需要同时考虑电学、热学、力学等多物理场效应,进行电热协同、热电协同等分析优化。

- 人工智能与机器学习应用:AI/ML技术正被用于加速布局、预测拥塞和优化PPA,实现设计空间探索的自动化和智能化。

- Chiplet与先进封装:随着Chiplet(芯粒)和2.5D/3D集成电路技术的发展,后端设计范畴扩展至硅中介层、微凸块和硅通孔(TSV)的设计与协同,涉及系统级封装(SiP)的物理实现。

四、集成电路芯片设计服务生态

专业的集成电路设计服务公司或部门,提供从前端到后端的全流程或部分流程外包服务(如Turnkey或NRE模式),其服务价值体现在:

- 专业分工与效率提升:让芯片设计公司(Fabless)能专注于核心架构与算法,将复杂、工具依赖度高的物理实现交由专业团队,缩短开发周期。

- 技术积累与资源共享:服务商积累了跨工艺、跨应用的丰富设计经验、IP库和设计方法论,能有效规避设计风险。

- 成本优化:通过优化PPA,帮助客户降低芯片的制造成本和使用成本,提升产品竞争力。

- 全生命周期支持:服务不仅限于设计实现,还可能涵盖设计咨询、IP集成、流片支持、封装测试协同乃至量产后的良率提升支持。

五、

集成电路后端设计是将抽象逻辑转化为物理现实的桥梁,是确保芯片性能、可靠性和可制造性的核心环节。面对日益复杂的工艺和系统集成需求,后端设计技术持续演进,并与设计服务生态紧密结合,共同推动着全球半导体产业的创新与发展。掌握后端设计的核心流程与挑战,对于芯片设计工程师、项目管理者及产业投资者都至关重要。