随着半导体工艺不断向更先进节点迈进,超大规模集成电路的复杂度呈指数级增长,这使得芯片的可测试性成为设计流程中至关重要的一环。在2022年的行业培训与实践中,可测性设计技术及其在集成电路芯片设计与服务领域的应用,正以前所未有的深度和广度被探讨与实施。

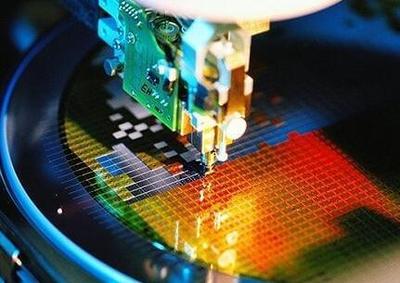

可测性设计是指在芯片设计阶段就预先考虑并植入测试结构,以确保芯片制造后能够被高效、低成本地测试,从而筛选出缺陷产品,保证出厂质量和可靠性。对于包含数十亿甚至上百亿个晶体管的超大规模集成电路,传统的测试方法已难以应对,DFT技术成为不可或缺的核心能力。

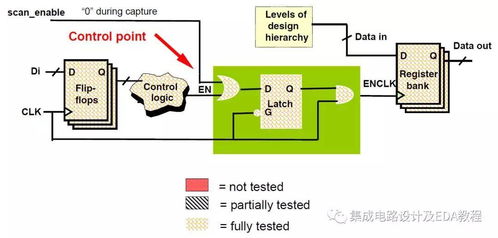

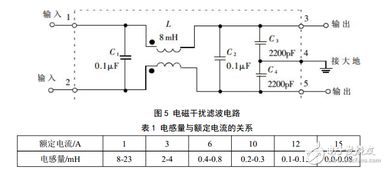

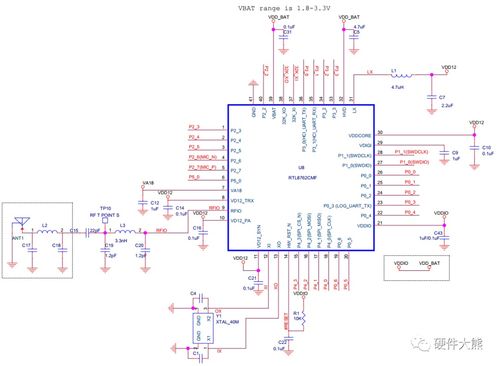

2022年的培训重点聚焦于几大主流DFT技术及其最新发展。扫描链设计仍是基础,但更强调针对低功耗设计和时序收敛的优化策略。内建自测试技术,特别是在存储器测试和逻辑核测试方面,其算法与硬件实现结构持续演进,以应对更复杂的故障模型。边界扫描技术不仅用于板级互联测试,在芯片封装和3D-IC堆叠测试中的作用也日益凸显。基于压缩的测试数据量缩减技术、测试功耗管理以及面向汽车电子等功能安全关键领域的DFT方法,都成为培训与实践中的热点。

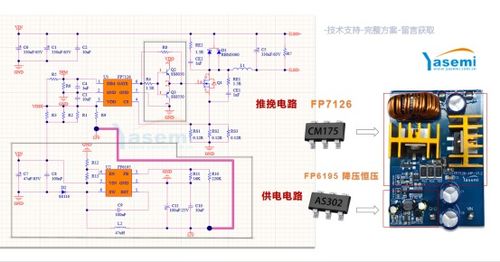

实践层面,DFT已深度融入从RTL设计到物理实现的完整设计流程。领先的芯片设计公司与服务提供商正构建高度自动化的DFT插入、验证和模式生成流程。培训中强调“左移”理念,即在设计早期就进行DFT规划与集成,以避免后期因测试问题导致的昂贵设计返工。云平台和机器学习技术开始被应用于DFT领域,例如利用AI优化测试向量、预测测试覆盖率以及进行智能诊断,从而进一步提升测试效率与质量。

对于集成电路芯片设计及服务产业而言,强大的DFT能力已成为衡量其技术成熟度和服务竞争力的关键指标。专业的DFT团队不仅能为客户设计出可测试性优异的芯片,还能提供从DFT架构咨询、设计实现到测试程序开发、生产测试支持的全流程服务。在2022年,随着芯片应用场景拓展至人工智能、自动驾驶、高性能计算等前沿领域,对DFT提出的挑战也更为严峻,相应的培训与实践也更加注重跨学科知识的融合与解决实际工程问题的能力培养。

总而言之,2022年围绕超大规模集成电路可测性设计的培训与实践,深刻反映了行业对芯片质量与可靠性的极致追求。DFT技术已从一项辅助技术演变为驱动芯片设计成功和制造盈利的核心支柱,持续推动着集成电路芯片设计及服务行业向更高水平迈进。