随着无线通信技术的飞速发展,射频集成电路(RFIC)在智能手机、物联网设备、卫星通信等领域的应用日益广泛。射频芯片的性能不仅取决于电路设计,其版图(Layout)设计同样至关重要,直接影响着芯片的噪声、增益、线性度、功耗乃至最终产品的成败。本文将结合一个典型的设计指导案例,系统阐述射频芯片Layout设计的核心原则,并探讨集成电路芯片设计及服务的完整流程。

一、 射频芯片Layout设计核心挑战与指导原则

与数字或低频模拟电路不同,射频芯片工作在GHz频段,其Layout设计需应对寄生效应、阻抗匹配、信号完整性、电磁干扰(EMI)和热管理等独特挑战。

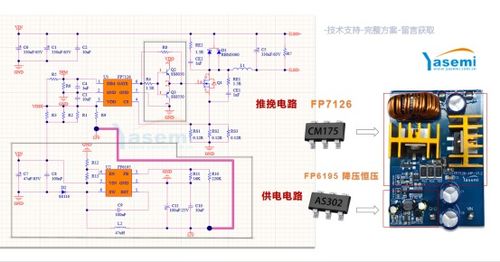

1. 案例背景:一款2.4GHz Wi-Fi前端模块的功率放大器(PA)设计

假设我们需要为一款集成化Wi-Fi芯片设计其功率放大器部分的版图。主要性能指标包括:输出功率23dBm,功率附加效率(PAE)大于35%,在给定工艺节点下实现。

2. 关键设计指导步骤与实践:

A. 衬底与工艺选择与建模:

- 指导原则: 优先选择具有高电阻率衬底(如SOI或特定化合物半导体)的工艺,以降低衬底损耗和噪声耦合。在深亚微米CMOS工艺中,需精确建立包括衬底耦合路径在内的寄生参数模型。

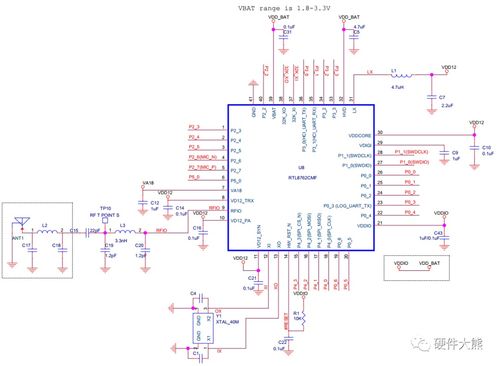

- 案例实践: 在本案例中,选用的是RF-CMOS工艺。设计初期,与晶圆代工厂紧密合作,获取准确的工艺设计套件(PDK),特别是高频下的器件模型、传输线模型和金属层堆叠的电磁特性数据。

B. 阻抗匹配网络布局:

- 指导原则: 匹配网络(通常由电感和电容构成)的布局必须紧凑,以最小化寄生电感和电阻。采用对称和共心布局来优化差分电路。

- 案例实践: 对于PA的输入、输出以及级间匹配,使用片上螺旋电感。布局时,将电感置于顶层厚金属以降低电阻,并确保电感之间、电感与有源区之间有足够的间距(利用屏蔽层或隔离槽)以防止磁耦合。匹配电容使用高密度MIM电容,并直接布设在需要连接的节点附近,避免长走线引入额外相移。

C. 信号路径与电源/地线设计:

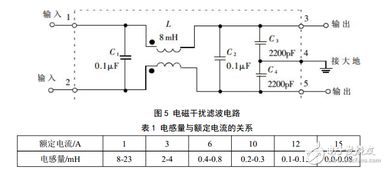

- 指导原则: 射频主信号路径应尽可能短、直,采用微带线或共面波导等可控阻抗互连。电源和地线必须“宽而短”,采用分布式去耦电容网络,并实现低阻抗回路。

- 案例实践: PA的射频输入输出走线采用顶层金属,宽度根据工艺提供的参数计算,以实现50欧姆特征阻抗。在电源线和地线布设中,采用网状结构(网格地),并在每个放大单元的电源引脚附近放置大量的片上深N阱去耦电容,以抑制高频噪声和维持电源完整性。关键信号路径下方布置实心接地屏蔽层。

D. 隔离与屏蔽:

- 指导原则: 对噪声敏感电路(如低噪声放大器LNA)与大功率或数字开关电路进行物理隔离。使用保护环、隔离槽和屏蔽墙。

- 案例实践: 在芯片布局规划时,将PA与内部的数字控制逻辑、频率合成器等模块分置于芯片两端,中间用隔离的电源域和物理间距隔开。在PA自身周围,用密集的衬底接触和N阱保护环包围,以吸收少数载流子并降低衬底噪声耦合。

E. 热设计:

- 指导原则: 功率器件均匀分布,避免热点;利用多层金属并联和散热通孔(Via)将热量传导至芯片表面。

- 案例实践: PA的末级大尺寸晶体管阵列被拆分成多个指状交叉排列的单元,并通过顶层金属和大量通孔阵列进行互连和散热。在芯片封装选型时,已提前考虑采用导热性能良好的封装(如QFN),并在芯片背面规划了热耦合路径。

F. 后仿真与验证:

- 指导原则: 必须进行包含所有寄生参数的电磁(EM)仿真和电-热协同仿真。

- 案例实践: 完成初步布局后,提取整个PA模块(包括电感、互连线)的寄生参数网表,进行后仿真。使用EM仿真工具对关键无源网络进行三维全波分析,确保其性能与原理图设计一致。仿真结果用于迭代优化布局,直至满足所有性能指标。

二、 集成电路芯片设计及一体化服务流程

成功的射频芯片设计远不止于版图。它需要一个贯穿始终、专业协同的服务体系:

- 系统定义与架构设计: 根据市场需求确定芯片规格。服务内容包括系统级建模、链路预算分析、架构选型(如零中频、超外差)。

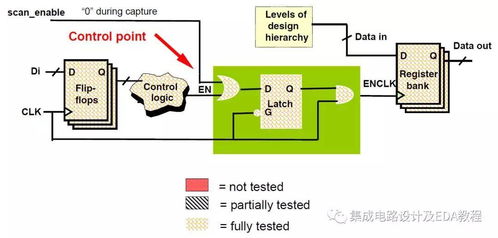

- 电路设计与仿真: 使用EDA工具进行晶体管级电路设计、前仿真、工艺角分析和蒙特卡洛分析,确保电路鲁棒性。

- 版图设计与验证: 如前文所述,执行严格的物理实现,并进行设计规则检查(DRC)、版图与电路图一致性检查(LVS)以及天线效应检查等。

- 后仿真与签核: 这是确保设计成功的最后技术关口。进行寄生参数提取后的全芯片仿真,包括射频性能、电源完整性和信号完整性分析。

- 流片与封装协同设计: 与代工厂和封装厂协作,完成掩模版制作、晶圆制造。封装设计需与芯片Layout同步,考虑引脚排布、键合线电感、封装寄生对射频性能的影响。

- 测试与量产支持: 提供测试方案设计、测试板开发、晶圆测试和成品测试服务。协助客户解决量产中的良率问题并提供持续的技术支持。

结论

射频芯片的Layout设计是一门结合了电磁场理论、半导体工艺和工程实践的艺术。通过本文的案例可以看出,从精确的工艺模型到细致的阻抗控制,从严格的隔离屏蔽到系统的热管理,每一个细节都关乎最终性能。而将优秀的Layout设计置于一个完整的“集成电路芯片设计及服务”流程中,从前端定义到后端量产支持,才能确保射频芯片从设计图纸成功走向商业应用,在激烈的市场竞争中占据先机。对于设计团队而言,深谙工艺特性、善用EDA工具、秉持严谨的工程规范,是驾驭射频版图复杂性的不二法门。